Memory

NAND FLASH

隨著人工智慧(AI)應用持續擴展,資料中心與 AI 伺服器對次世代儲存產品的需求不斷攀升。

新一代 NAND Flash 記憶體具備大容量、高傳輸速度、高效能與低功耗等特性,可在斷電狀態下保存資料,廣泛應用於 USB、SD 卡與 SSD 等產品。

目前 3D NAND 的堆疊層數已由 200~300 層持續提升,預期未來將發展至 500~600 層以上。因此,3D NAND 亦如同 DRAM,逐步導入高並行與大型混合鍵合(Hybrid Bonding)等先進製程技術。此一技術演進同時帶來多項挑戰,包括 Cell 電流控制、新設備與新製程開發、Stress/Warpage 補償技術、零缺陷混合鍵合,以及 X–Y 單元微縮等關鍵課題。

KI 正與全球頂尖晶片製造商攜手推動技術開發,以因應 NAND Flash 晶片在更高整合度與更高速發展趨勢下,持續成長的 I/O 測試需求。

DRAM 與 HBM

隨著人工智慧(AI)應用加速發展,資料中心與 AI 伺服器對次世代記憶體產品的需求持續攀升。此類高頻寬記憶體解決方案須同時滿足大容量、更高運算效能、更高能源效率以及低功耗等關鍵需求。

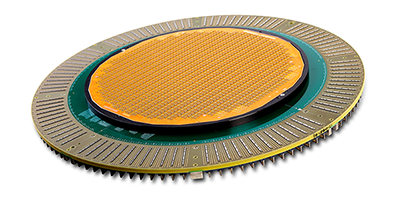

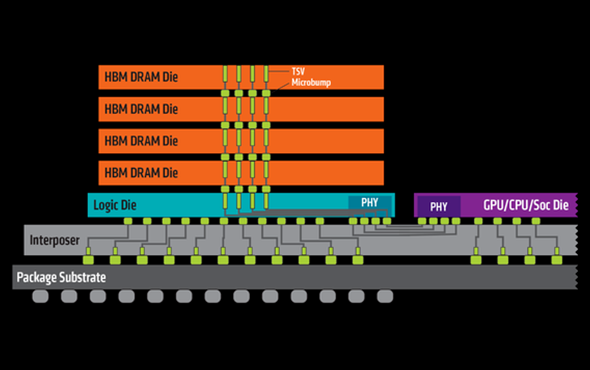

高頻寬記憶體(HBM)係透過 TSV(Through-Silicon Via)技術,將多顆 DRAM 晶片進行垂直堆疊,以大幅提升資料處理頻寬。過往 HBM 主要採用熱壓縮(TC)鍵合方式,在 DRAM Die 之間以微凸塊(Micro Bump)進行連接,使 HBM 堆疊層數發展至 16 層或 20 層時,逐漸面臨製程與結構上的限制。在有限的 HBM 封裝厚度(最高約 775 μm)條件下,即使減薄 DRAM Die,仍難以突破進一步堆疊的瓶頸。

為克服上述限制,DRAM 製造商已開發於晶片與晶片之間實現銅對銅直接互連的混合鍵合(Hybrid Bonding)技術。 此技術可移除微凸塊,大幅降低 HBM 封裝厚度,同時實現次世代 AI 工作負載所需的更高 I/O 密度與更佳散熱效能。

KI 緊跟上述技術發展趨勢,自早期階段即與客戶展開深度合作,積極支援以混合鍵合為核心的 HBM 解決方案快速導入與量產。